Research

Device-Circuit-Layout Co-design for sub-10nm technologies

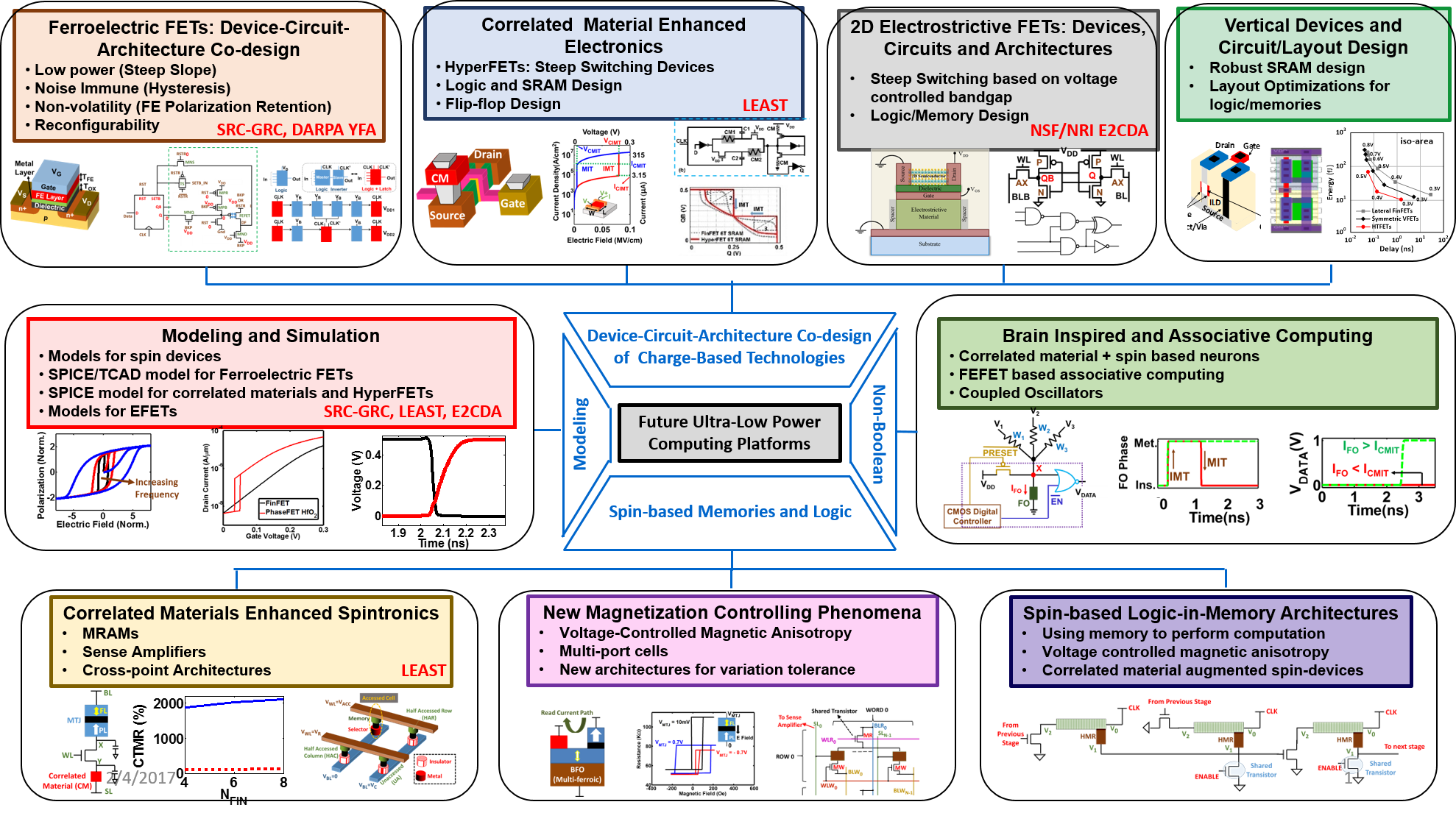

As the transistors scale beyond 10nm technology, there is a strong need for the exploration of advanced transistor architectures coupled with novel circuit and layout techniques to sustain the benefits of technology scaling. At ICDL, we are developing co-design methodologies with an objective to perform circuit/layout-aware device optimization and design memories and logic taking into account the unique properties of the advanced transistors. Layout methodologies are being explored to counter issues like increase in the source/drain resistance and parasitic capacitances. We are also exploring circuit and device level techniques for near-threshold operation.

Steep- Switching Technologies

Steep-switching devices have garnered an immense interest due to the possibilities of beating the Boltzmann’s limit of 60mV/decade sub-threshold swing (at room temperature) associated with conventional transistors. However, these technologies have their own overheads, due to which their benefits at the circuit/system level are not entirely clear. The goal of this research program is to thoroughly analyze the circuit implications of the steep switching technologies and develop novel circuit design techniques to harness their full potential. Definition of the material and device design space taking into consideration the cir1cuit requirements is a key component of this research.

Spin-based Memory and Logic Design

Spin-based storage has emerged as a promising alternative to standard charge-based memories due to zero array stand-by leakage, non –volatility and high integration density. However, low write efficiency and self-conflicting design requirements for read and write make it challenging to design low power robust spin-memories. At ICDL, we are exploring novel techniques at the device, circuit and array level to counter the issues associated with spin-based storage. This includes the device-circuit-array co-design for memories employing voltage based magnetization switching phenomena, development of variation-tolerant design methodologies for memories with separate read-write paths and techniques to enhance the magneto resistance. We are also exploring spin-based logic based on multi-terminal spin devices.

Modeling, Simulations and Technology Benchmarking

A key component of our research at ICDL is the development of physics-based and compact models for emerging devices for device-circuit analysis. The technologies that we are currently modeling include charge-based devices, spin devices and steep switching devices. Various models are integrated in a device-circuit simulation framework, which enables us to analyze the circuit implications of the emerging technologies and perform device-circuit co-design for low power robust memories and logic. We are also working on developing a benchmarking framework for new technologies based on extensive circuit and device simulations, which will provide useful insights into their benefits and overheads.